Armv7에서는 프로세서의 상태 정보를 저장하는 CPSR, SPSR 레지스터를 제공합니다. 먼저 CPSR 레지스터를 설명하고 CPSR 레지스터를 백업하는 용도로 설계된 SPSR 레지스터에 대해서 알아봅시다.

CPSR 레지스터

CPSR은 Current Program Status Register의 약자로 프로세서의 상태 정보를 저장하는 레지스터입니다. 먼저 CPSR 레지스터의 비트 맵 정보를 알아봅시다.

그림 2.2 CPSR 레지스터의 비트 맵

CPSR 레지스터를 구성하는 비트 맵에서 주로 Conditional Flags, Mask Bit 그리고 M[4:0]이 사용됩니다. 먼저 Conditional Flags를 알아봅시다.

Condition Flags: bits[31:28]

조건 플래그는 명령어를 연산한 후 설정되는 플래그입니다. 다음 표를 보면 각 플래그가 어느 조건에서 업데이트되는지 알 수 있습니다.

표 2.2 CPSR 레지스터의 Condition flags의 역할

Arm 코어는 옵코드(Opcode)를 페치하고 난 다음에 이를 무조건 실행하지 않습니다. 위에서 명시된 컨디셔널 플래그를 참고해 다음 주소에 있는 명령어이 실행됩니다. 한 가지 예를 들까요?

01 cmp r0,#0x0 ; r0,#0

02 beq 0x80101064 ; no_work_pending

03 movlt r7,#0x0 ; r7,#0

01번재 줄에서는 r0 레지스터의 값과 0x0을 비교합니다. 01번째 줄의 명령어를 실행하면 CPSR 레지스터의 Z 비트가 업데이트되는데, 이 값을 보고 02번째 줄이 다른 방식으로 실행됩니다.

[정보]

CPSR 레지스터를 구성하는 비트 맵의 정보만 파악하면 배운 내용을 활용하기 어렵습니다. CPSR의 비트 정보를 활용해 명령어의 실행 흐름을 어떤 방식으로 제어하는지를 파악하는게 더 중요합니다.

Mask bits, bits[8:6]

마스크 비트는 익셉션과 인터럽트를 마스크(비활성화)할 때 사용됩니다. 각 마스크 비트가 어떤 조건에서 활성화되는지는 다음 항목을 보면 알 수 있습니다.

* A, bit[8]: Asynchronous 어보트를 비활성화

* I, bit[7]: IRQ를 비활성화

* F, bit[6]: FIQ를 비활성화

위에서 정의된 마스크 비트를 1로 설정하면 해당 기능이 비활성화됩니다.

M[4:0], bits[4:0]

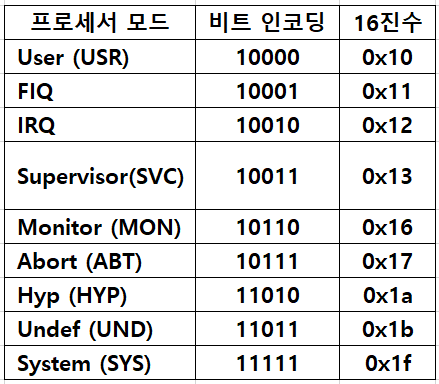

CPSR 레지스터는 Arm의 동작 모드를 나타내는 비트를 저장하며 이를 CPSR.M으로 표기합니다.

Arm 동작 모드별로 M[4:0]은 다음과 같은 비트 정보를 저장합니다.

표 2.3 Arm 모드 별 비트 인코딩 값

동작 모드를 나타내는 비트 값은 많은 코드에서 확인할 수 있으니 잘 익혀둘 필요가 있습니다.

.

'시스템 소프트웨어 개발을 위한 Arm 아키텍처의 구조와 원리 > 3장: 레지스터' 카테고리의 다른 글

| [Arm프로세서] Armv8: 범용(General Purpose) 레지스터란 (0) | 2023.06.10 |

|---|---|

| [Arm프로세서] Armv7: SPSR(Saved Program Status Register) 레지스터란 (0) | 2023.06.10 |

| [Arm프로세서] Armv7: 범용 레지스터에서 뱅크드 레지스터란 (0) | 2023.06.10 |

| [Arm프로세서] Armv7: 범용(General Purpose) 레지스터란 (0) | 2023.06.10 |

| [Arm프로세서] Arm 아키텍처의 레지스터 소개 (0) | 2023.06.10 |