Armv8 아키텍처에서 정의된 레지스터 중 SP_ELn와 X30 레지스터는 AAPCS와 연관된 핵심 레지스터입니다. 먼저 전체 레지스터 목록 중에서 SP_ELn와 X30 레지스터를 보겠습니다.

전체 레지스터 목록 중 SP_ELn와 X30 레지스터

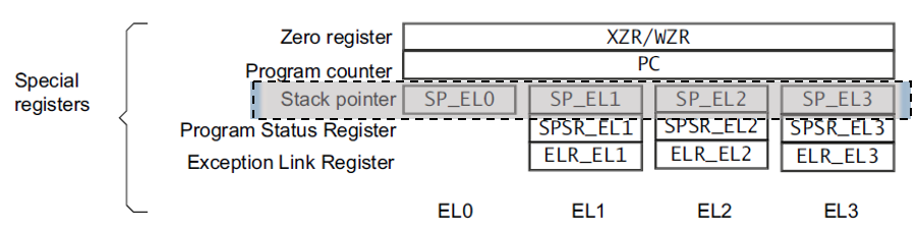

다음 그림을 보면서 Armv8 아키텍처에서 정의된 레지스터 중 AAPCS와 연관된 레지스터를 알아봅시다.

사진 설명을 입력하세요.

그림 7.1 Armv8 아키텍처의 레지스터 목록 중 AAPCS와 연관된 레지스터

(출처: ARMv8-A-Programmer-Guide.pdf)

위 그림은 Armv8 아키텍처에서 정의된 레지스터 목록입니다. 그림에서 빗금으로 표기된 박스를 보겠습니다.

SP_EL1는 익셉션 레벨1에서 실행되는 SP 레지스터, SP_EL0은 익셉션 레벨0에서 실행되는 SP 레지스터를 의미합니다. 또한 하이퍼바이저가 실행되는 EL2에서 실행되는 SP 레지스터는 SP_EL2로 표기합니다.

[정보]

Armv8 아키텍처에서는 SP 레지스터를 SP_ELn으로도 표기합니다.

일반적으로 다음과 같은 명령어를 실행하면 이를 어떻게 해석해야 할까요?

sub sp, sp, #4

Armv8 아키텍처의 어셈블리 명령어에서 sp와 같이 표기됐으면 해당 어셈블리 명령어를 실행하는 익셉션 레벨을 기준으로 해석하면 됩니다.

만약 위 명령어를 실행하는 익셉션 레벨이 EL1이면 SP_EL1을 의미하고, EL2이면 SP_EL2를 의미합니다.

예를 들어 운영체제 커널은 EL1에서 실행되므로, 커널 공간에 있는 프로세스의 SP 레지스터는 SP_EL1에서 확인할 수 있습니다. 유저 애플리케이션은 EL0에서 실행되므로, 유저 프로세스의 SP 레지스터는 SP_EL0에서 확인할 수 있습니다.

다음으로 X30 레지스터는 링크 레지스터를 뜻하며, 서브 루틴을 호출한 다음에 복귀한 주소를 저장하는 역할을 수행합니다. Armv7 아키텍처의 링크 레지스터인 R14와 같은 기능입니다.

SP_ELn 아랫 부분에 표기된 레지스터를 보겠습니다.

프로세서의 상태를 저장하는 SPSR(Saved Processor State Register) 레지스터와 ELR(Exception Link Register) 레지스터가 있습니다. 이 레지스터도 익셉션 레벨 별로 정의돼 있습니다. 이 레지스터는 AAPCS와는 직접적인 연관은 없지만 익셉션이 유발돼 익셉션 레벨이 변경될 때 이전 상태로 복귀하기 위한 용도로 쓰입니다.

Arm 스팩 문서에서 본 SP 레지스터

이번에는 Arm 스팩 문서를 보면서 SP와 X30 레지스터에 대해 조금 더 알아봅시다. 먼저 SP 레지스터를 살펴봅시다.

4.1.2 Stack pointer

In the ARMv8 architecture, the choice of stack pointer to use is separated to some extent from the Exception level. By default, taking an exception selects the stack pointer for the targetException level, SP_ELn.

For example, taking an exception to EL1 selects SP_EL1. Each Exception level has its own stack pointer, SP_EL0, SP_EL1, SP_EL2, and SP_EL3.

[출처: Programmer’s Guide for ARMv8-A]

위 스팩 내용에서 중요한 부분은 다음과 같이 정리할 수 있습니다.

* 익셉션 레벨 별로 스택이 존재하는데, 이 스택 주소를 저장하는 SP_ELn 레지스터가 있다.

* 예를 들어 SP_EL0, SP_EL1, SP_EL2, and SP_EL3와 같은 스택 포인터 레지스터가 존재한다.

여기서 말하는 스택은 프로세스가 사용하는 스택을 의미합니다. Armv8에서 정의된 SP_ELn 레지스터도 프로세스의 스택 구간 내의 주소 구간 내에서 업데이트됩니다.

Arm 스팩 문서에서 본 링크 레지스터: X30

이어서 X30 레지스터를 스팩 문서 분석을 통해 알아봅시다.

6.4 Flow control

Calls to subroutines, where it is necessary for the return address to be stored in the link register (X30), use the BL instruction. This does not have a conditional version. BL behaves as a B instruction with the additional effect of storing the return address, which is the address of the instruction after the BL, in register X30.

[출처: Programmer’s Guide for ARMv8-A]

X30 레지스터를 명쾌하게 설명한 문장인데요. 요약하면 다음과 같습니다.

* X30은 BL 명령어와 함께 주소나 함수로 분기했을 때 서브 루틴에서 복귀할 주소를 저장하는 레지스터이다.

Armv7 아키텍처에서는 R14가 각 Arm 모드 별로 존재했습니다. R14는 서브 루틴(함수 호출)을 호출할 때 복귀할 주소뿐만 아니라, 익셉션이 유발된 후 복귀할 주소를 저장했습니다.

그런데 Armv8 아키텍처에서는 익셉션이 발생한 후 복귀할 주소를 저장하는 익셉션 링크 레지스터(ELR: Exception Link Register)를 익셉션 레벨 별로 따로 정의합니다. 그래서 Armv8 아키텍처에서 X30는 익셉션 레벨 별로 존재하지 않습니다.

이처럼 SP와 X30 레지스터는 Armv8 아키텍처에서 정의된 레지스터와는 다른 레지스터와는 달리 서브 루틴을 호출하기 위한 사용됩니다.

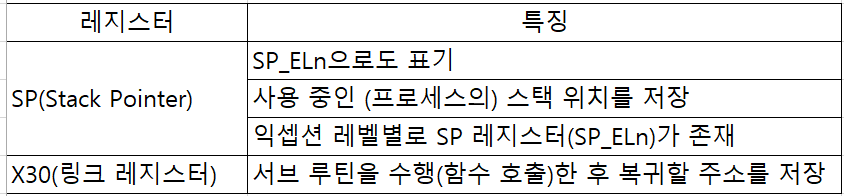

이번 절에 소개한 SP_ELn와 X30 레지스터를 표로 정리해 보겠습니다.

사진 설명을 입력하세요.

표 7.1 SP_ELn와 X30 레지스터의 특징

어셈블리 명령어 중에서 SP_ELn와 X30레지스터를 보면, 위 표의 내용이 머리에 자동으로 떠올랐으면 좋겠습니다.

'시스템 소프트웨어 개발을 위한 Arm 아키텍처의 구조와 원리 > 13장: Armv8 - AAPCS' 카테고리의 다른 글

| [Arm프로세서] AAPCS: Armv8: 함수를 호출하기 위한 디자인 (0) | 2024.12.24 |

|---|---|

| [Arm프로세서] AAPCS: Armv8 아키텍처에서 AAPCS 관련 레지스터 (0) | 2024.12.22 |

| [Arm프로세서] Armv8 - 링크 레지스터: X30 (0) | 2024.01.19 |

| [Arm프로세서] Armv8 - SP_ELn과 X30 레지스터란? (0) | 2024.01.19 |

| [Arm프로세서] Armv8 - AAPCS 관련 레지스터 (0) | 2024.01.17 |