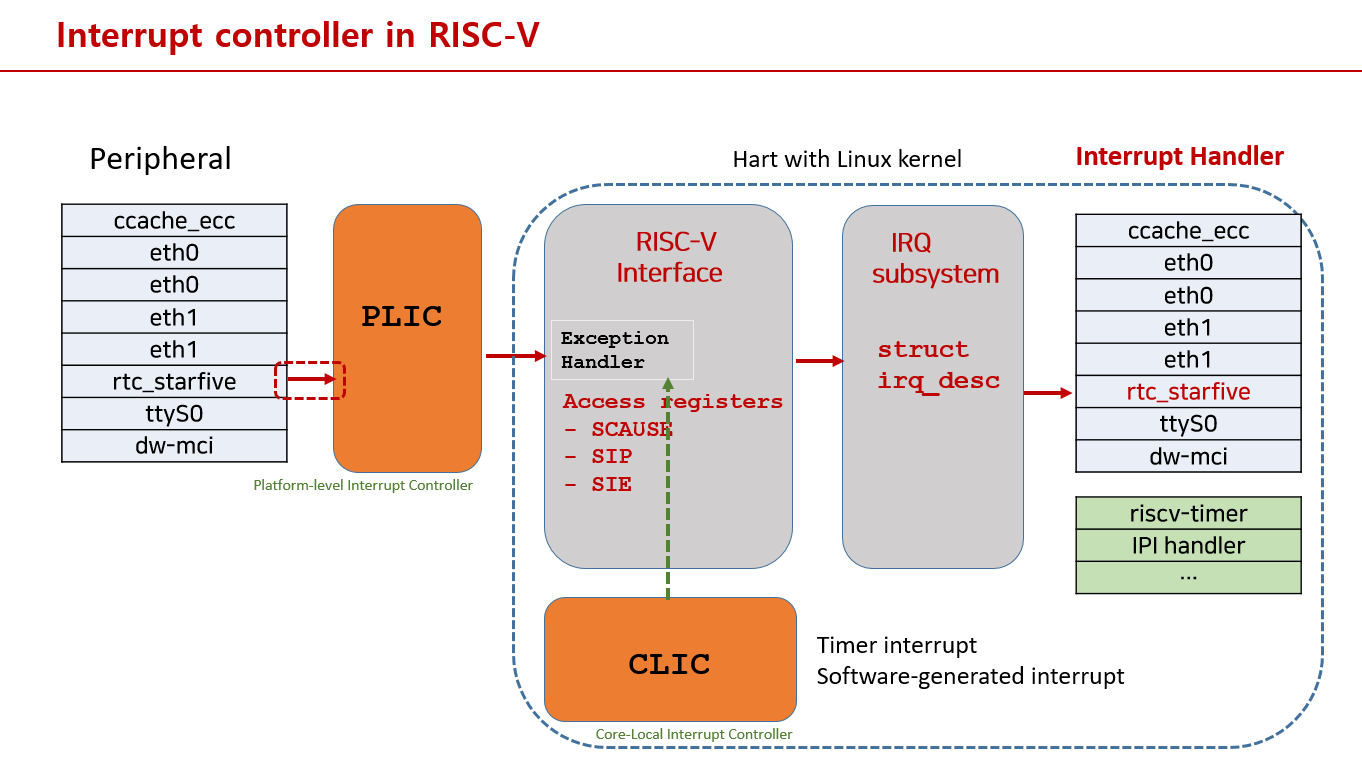

RISC-V 아키텍처에서는 2가지 타입의 인터럽트 콘트롤러가 있다:

- PLIC (Platform-level Interrupt Controller)

- CLIC (Core-local Interrupt Controller)

아래 그림을 보면서 전체 구조를 확인하자:

PLIC는 외부 퍼리퍼럴 디바이스에서 유발되는 인터럽트를 받아서, RISC-V Hart에 전달(Routing)하는 역할을 한다. RISC-V Hart(Core)는 인터럽트가 유발됐다는 사실을 확인한 후, 익셉션을 유발한다.

CLIC는 RISC-V Hart 내부에 존재한다. 타이머나 Software generated interrupt를 유발하는데 주로 사용된다. CLIC를 통해서 인터럽트가 유발되면 RISC-V Hart는 역시 익셉션을 유발한다.

퍼리퍼럴에서 인터럽트가 유발되면 처리되는 실행 흐름을 알아보자:

[1]: 여러 퍼리퍼럴 디바이스에서 인터럽트를 유발한다. 여기서 말하는 인터럽트는 전기적인 신호이다.

[2]: PLIC 내부는 게이트웨이와 PLIC 코어로 구성된다. 게이트웨이가 물리적인 인터럽트 신호를 PLIC 내부에서 관리할 수 있도록 변환한 다음에, PLIC 코어에서 인터럽트를 RISC-V Hart에 라우팅한다.

[3]: RISC-V Hart는 익셉션을 유발한다. SCAUSE 레지스터의 가장 높은 비트를 1로 설정하고 익셉션 코드는 9로 설정한 다음에 익셉션 벡터 주소로 PC를 브랜치한다.

[4]: 인터럽트는 CPU 아키텍처에 의존적인 동작을 한다. 리눅스 커널은 CPU 아키텍처에 dependent하지 않는 소프트웨어 레이어를 가져간다. IRQ 서브 시스템에서 해당 인터럽트에 대한 정보(struct irq_desc)를 읽어서, 해당 인터럽트를 핸들링하는 인터럽트 핸들러 함수를 호출한다.

[5]: 해당 인터럽트에 대응되는 인터럽트 핸들러가 호출된다. 예를 들어 rtc_starfive라는 인터럽트가 유발되면 rtc_starfive를 핸들링하는 인터럽트 핸들러 함수가 호출된다.

디바이스 드라이버를 개발하는 개발자들은 PLIC의 구조를 잘 알아야 할 필요가 있다. 대부분 퍼리퍼럴 디바이스는 인터럽트를 통해 하드웨어적인 변화를 알리기 때문이다.

상세한 동작 방식은 아래 강의 영상을 참고하세요:

'RISC-V > 인터럽트 콘트롤러' 카테고리의 다른 글

| [RISC-V] 리눅스 커널 - local_irq_enable() 함수의 역할과 sstatus.sie (로컬 인터럽트 설정) (0) | 2025.03.29 |

|---|